# TECHNOLOGIE ET EMBALLAGE DE PUCES DE TSMC: VERS UNE PUISSANCE DE CALCUL ACCRUE

Au Symposium technologique nord-américain de TSMC, la société a détaillé ses cartes routières technologiques pour les semi-conducteurs et l’emballage de puces. Alors que la première est essentielle pour maintenir la partie traditionnelle de la loi de Moore, la seconde pourrait accélérer une tendance vers des processeurs fabriqués à partir de plus en plus de silicium, conduisant rapidement à des systèmes de la taille d’une galette de silicium entière. Par exemple, le prochain carreau d’entraînement de nouvelle génération Dojo de Tesla est déjà en production, affirme TSMC. Et en 2027, la fonderie prévoit d’offrir une technologie pour des systèmes à l’échelle de galettes plus complexes que ceux de Tesla, capable de fournir 40 fois plus de puissance de calcul que les systèmes actuels.

# VERS UNE INTÉGRATION À L’ÉCHELLE DE LA GALETTE

Pendant des décennies, les fabricants de puces ont augmenté la densité de la logique sur les processeurs principalement en réduisant la surface occupée par les transistors et la taille des interconnexions. Mais ce schéma atteint ses limites. Ainsi, l’industrie se tourne vers une technologie d’emballage avancée qui permet à un seul processeur d’être fabriqué à partir d’une plus grande quantité de silicium. La taille d’une puce unique est limitée par le plus grand motif que l’équipement de lithographie peut produire, actuellement d’environ 800 millimètres carrés. Donc, si vous voulez plus de silicium dans votre GPU, vous devez le fabriquer à partir de deux ou plusieurs matrices. La clé est de connecter ces matrices de sorte que les signaux puissent passer de l’une à l’autre aussi rapidement et avec aussi peu d’énergie que s’ils étaient tous une seule pièce de silicium.

# UNE TECHNOLOGIE D’EMBALLAGE AVANCÉE

TSMC fabrique déjà un accélérateur d’IA à la taille d’une galette pour Cerebras, mais cet arrangement semble être unique et différent de ce que TSMC propose maintenant avec ce qu’il appelle Système-sur-Galette.

En 2027, vous obtiendrez une intégration à l’échelle de la galette qui offre 40 fois plus de puissance de calcul, plus de silicium qu’avec plus de 40 motifs et de la place pour plus de 60 puces de mémoire à haute bande passante, prédit TSMC.

# LA TECHNOLOGIE DE CONCEPTION

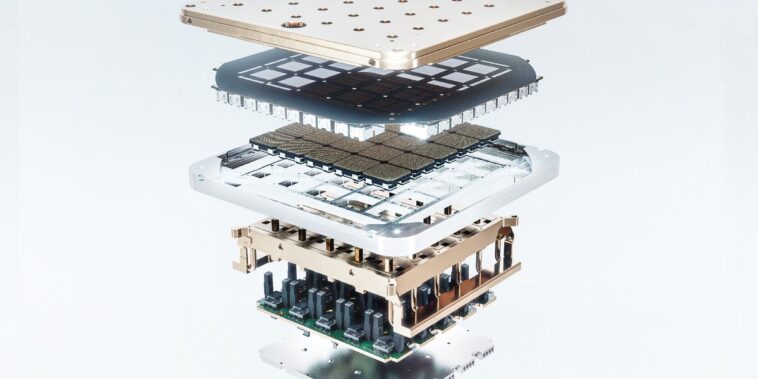

Avec sa première série de Système-sur-Galette, TSMC offre une solution différente aux problèmes à la fois de la limite du motif et du rendement. Le processus commence avec des matrices de logique déjà testées pour minimiser les défauts. Ces matrices sont placées sur une galette de support, et les espaces vides entre les matrices sont comblés. Ensuite, une couche d’interconnexions à haute densité est construite pour connecter la logique en utilisant la technologie d’étalement intégrée de TSMC. L’objectif est de rendre la bande passante des données entre les matrices si élevée qu’elles agissent efficacement comme une seule grande puce.

# L’AVENIR DE LA TECHNOLOGIE À L’ÉCHELLE DE LA GALETTE

En 2027, TSMC prévoit d’offrir une intégration à l’échelle de la galette basée sur sa technologie d’emballage plus avancée, la puce-sur-galette-sur-substrat (CoWoS). Dans cette technologie, la logique prétestée et, surtout, la mémoire à haute bande passante, sont fixées à un substrat de silicium qui a été modelé avec des interconnexions à haute densité et traversé par des connexions verticales appelées voies à travers le silicium. Les puces logiques attachées peuvent également tirer parti de la technologie de TSMC appelée système-sur-puces intégrées en 3D (SoIC).

Le passage à l’échelle de la galette est l’aboutissement logique d’une expansion de la technologie d’emballage déjà visible dans les GPU haut de gamme. Le prochain GPU de Nvidia, Blackwell, utilise CoWos pour intégrer plus de 3 motifs, y compris 8 puces de mémoire à haute bande passante. D’ici 2026, l’entreprise prévoit d’étendre cela à 5,5 motifs, dont 12 puces de mémoire HB. TSMC affirme que cela se traduirait par plus de 3,5 fois plus de puissance de calcul que ce que permet sa technologie de 2023.

# APPLICATIONS DE L’ÉCHELLE DE LA GALETTE

La version de 2027 du système-sur-galette ressemble dans une certaine mesure à la technologie appelée Fabric Interconnect Silicon, ou Si-IF, développée à l’UCLA il y a plus de cinq ans. L’équipe derrière SiIF comprend le professeur de génie électrique et informatique Puneet Gupta et le Fellow de l’IEEE Subramanian Iyer, qui est chargé de mettre en œuvre la portion d’emballage du CHIPS Act des États-Unis.

Ils travaillent à rendre les interconnexions sur la galette plus denses et à ajouter d’autres fonctionnalités à la technologie. “Si vous voulez que cela soit une infrastructure technologique complète, cela doit faire beaucoup d’autres choses en plus de fournir une connectivité fine”, déclare Gupta, également Fellow de l’IEEE. “L’un des plus gros points de friction pour ces grands systèmes sera la distribution de l’énergie.” L’équipe de l’UCLA travaille donc sur des moyens d’ajouter des condensateurs et des inductances de bonne qualité au substrat de silicium et d’intégrer des transistors de puissance en nitrure de gallium.

L’entraînement de l’IA est la première application évidente pour la technologie à l’échelle de la galette, mais ce n’est pas la seule, et ce n’est peut-être pas la meilleure, déclare l’architecte en informatique de l’Université d’Illinois Urbana-Champaign et Fellow de l’IEEE Rakesh Kumar. À l’International Symposium on Computer Architecture en juin, son équipe présente la conception d’un commutateur réseau à l’échelle de la galette pour les centres de données. Un tel système pourrait réduire le nombre de commutateurs réseau avancés dans un très grand centre de données de 16 000 racks de 4 608 à seulement 48, rapportent les chercheurs. Un centre de données de taille beaucoup plus petite pour environ 8000 serveurs pourrait se contenter d’un seul commutateur à l’échelle de la galette.

**Sources:**

– [IEEE](https://spectrum.ieee.org/)

– [TSMC](https://www.tsmc.com/english/index.htm)