# Revolution dans la conception de processeurs : les transistors Forksheet pour pallier les limites des nanosheets

Les constructeurs les plus réputés de processeurs se trouvent en ce moment en plein remaniement de leur architecture de dispositif sur une décennie, avec la transition des *finFETs* aux *nanosheets*. Une autre transformation essentielle se produira en 10 ans, où les dispositifs de nanosheets seront empilés les uns sur les autres pour former des *transistors FET complémentaires*, capables de réduire la taille de certains circuits de moitié. Cependant, cette dernière évolution sera difficile à réaliser, selon les experts. Un autre type de transistor, appelé *Forksheet*, pourrait aider à réduire la taille des circuits sans nécessiter des travail trop important.

L’idée du Forksheet est née de l’étude des limites de l’architecture des nanosheets, selon Julian Ryckaert, vice-président des technologies logiques chez Imec. La caractéristique principale des nanosheets est leurs piles horizontales de rubans de silicium entourées d’une porte de contrôle de courant. Bien que les nanosheets ne soient entrées en production que récemment, les experts cherchaient déjà leurs limites il y a plusieurs années. Imec a été chargé de déterminer à partir de quel moment les nanosheets atteindront leurs limites.

L’équipe de Ryckaert a découvert que l’une des principales limitations pour réduire la logique basée sur les nanosheets est de maintenir la séparation entre les deux types de transistors qui composent la logique CMOS, NMOS et PMOS. Les deux types doivent maintenir une certaine distance pour limiter la capacité qui réduit les performances et la consommation d’énergie des appareils. “Le Forksheet est un moyen de briser cette limitation”, selon Ryckaert.

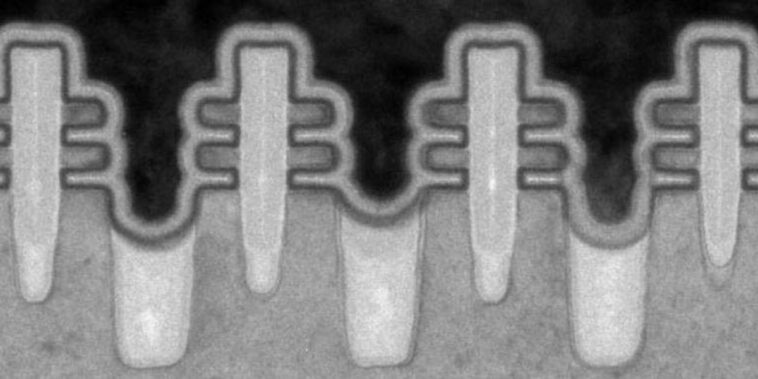

Au lieu de dispositifs individuels de nanosheets, le Forksheet construit des paires de nanosheets de chaque côté d’un mur diélectrique. Le mur permet de placer les dispositifs plus près les uns des autres sans causer de problème de capacité, selon Naoto Horiguchi, directeur de la technologie CMOS chez Imec. Les concepteurs pourraient utiliser l’espace supplémentaire pour réduire la taille des cellules logiques, ou ils pourraient utiliser la place supplémentaire pour construire des transistors avec des feuilles plus larges, améliorant ainsi leurs performances.

“CFT est probablement l’architecture CMOS finale”, déclare Horiguchi. Mais il ajoute que “l’intégration de CFT est très complexe”. Le Forksheet utilise la plupart des étapes de production des nanosheets, ce qui rendrait sa fabrication plus facile, selon lui. Imec prévoit d’avoir achevé son développement vers 2028.

Cependant, il reste encore de nombreux obstacles à franchir. “C’est plus compliqué que prévu”, a déclaré Horiguchi. Du point de vue de la fabrication, le mur diélectrique pose un peu de problèmes. Il existe plusieurs types de diélectriques utilisés dans les technologies récentes de CMOS, et la réalisation de Forksheet nécessite la suppression d’autres étapes sans endommager le mur. Et il reste à déterminer quels types de transistors doivent être utilisés de chaque côté du mur. L’idée initiale était de mettre un PMOS sur un côté et un NMOS de l’autre, mais il pourrait être avantageux d’utiliser le même type sur les deux côtés.

Ce qui est certain, c’est que les Forksheet représentent une forme innovante et prometteuse de consolidation des transistors en dépassant les limites découlant actuellement de la morphologie des nanosheets.